VHDLから作成

Last-modified: Tue, 01 Sep 2015 07:52:44 JST (3252d)

Top > VHDLから作成

- FPGAの回路を作成するのに、VHDLを書いて、それをFPGAに書き込む方法メモです。

ボードはBASYS2で、ISEのバージョンは14.7になります。

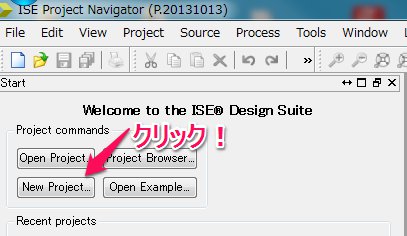

Projectの作成

- New Projectボタンを押し、新しいプロジェクトを作成します。

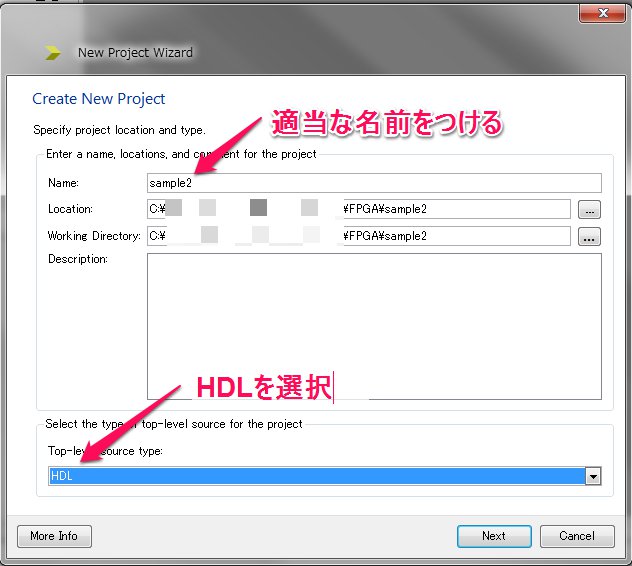

- 適当なプロジェクト名をつけ、Top-level source type:にはSchematicを選択します。

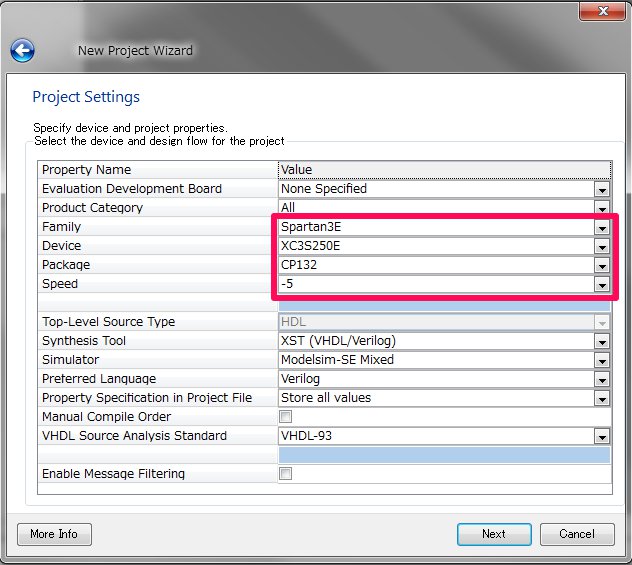

- Project Settingでは、本ボード(BASYS2)に搭載されているデバイス、パッケージなどを設定します。

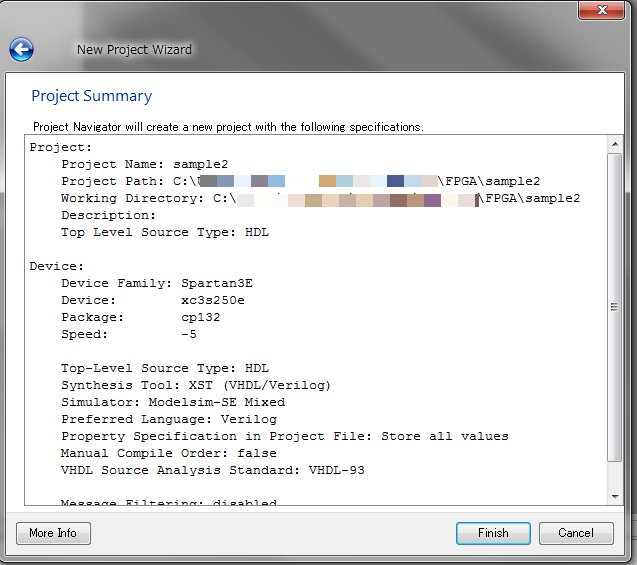

- サマリーが表示されます。Finishを押すとプロジェクトが作成されます。

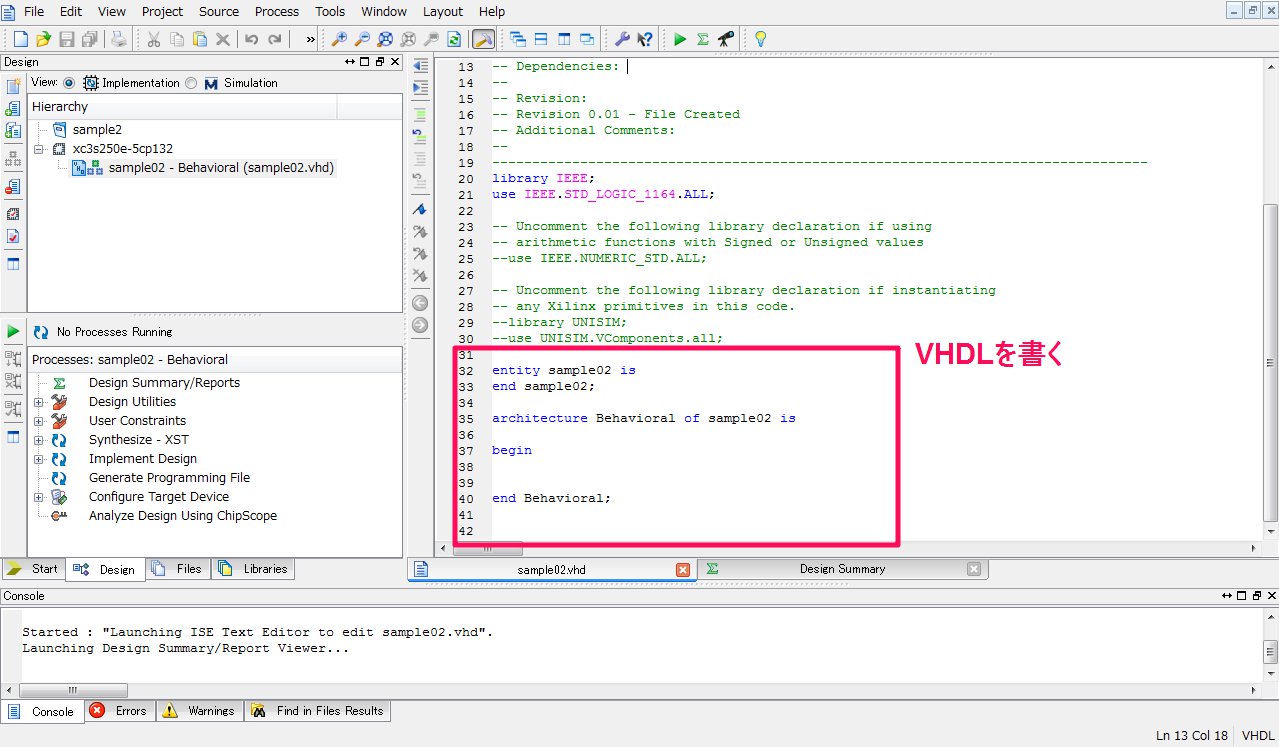

VHDLを書く

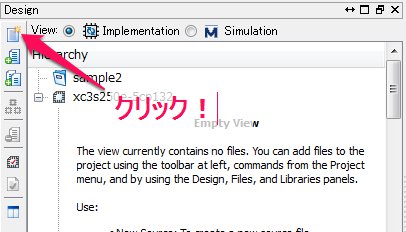

- 次に、VHDLを書いていきます。画面左端にある、New Sourceボタンを押します。

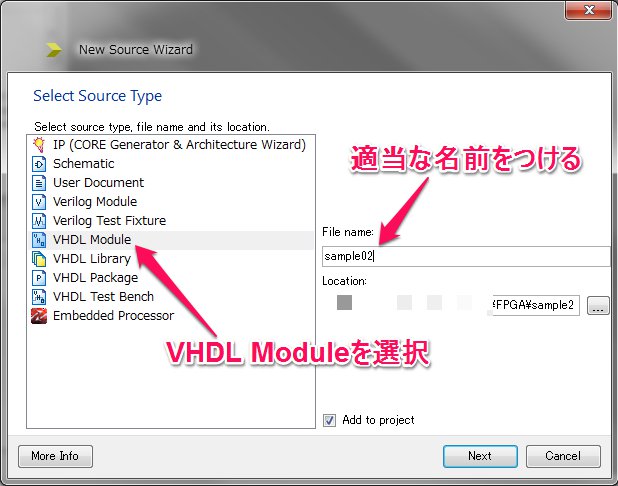

- 追加するソースファイルを設定します。ここではVHDLを追加するので、Source TypwにはVHDL Moduleを選択し、適当な名前をつけます。

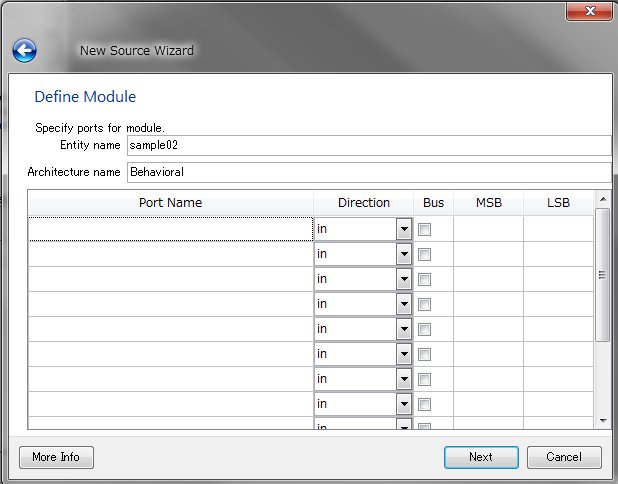

- 入出力が決まっている場合は、ここで指定すると、スケルトンコードが生成されます。直接コード中に記載しても良いので、ここでは特に何もしません。

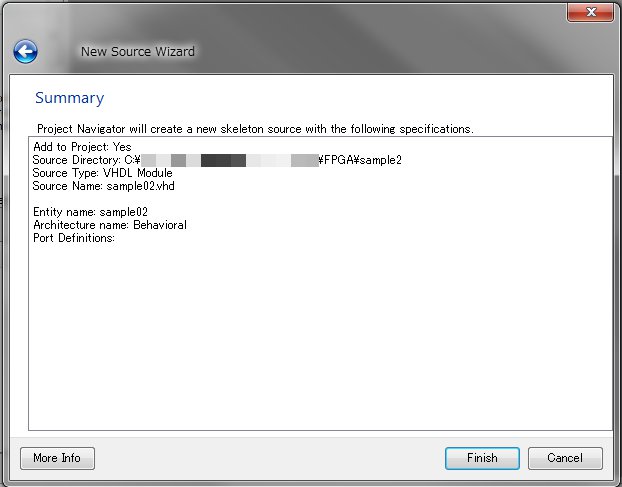

- サマリーが表示されます。Finishiを押すとファイルが追加されます。

- あとはひたすらVHDLを書きます。

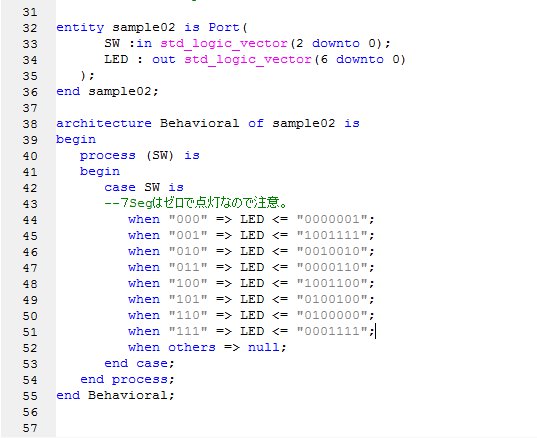

- ここでは、サンプルとして、スイッチからの3bit入力に対応する10進数を7SegLEDに表示するコードを書きます。

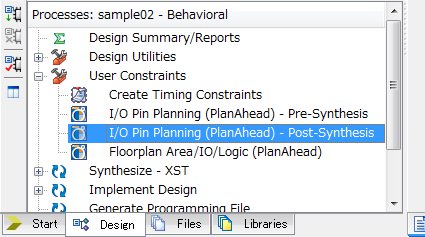

といいても、単純にスイッチのbitに対応する7SegのH/Lを書いただけです。 - 書き終えましたら、UserConstraintsの左端の+をクリックして展開し、その中にあるI/O Pin Plannning(PlanAhead)-Post-Synthesisをクリックします。

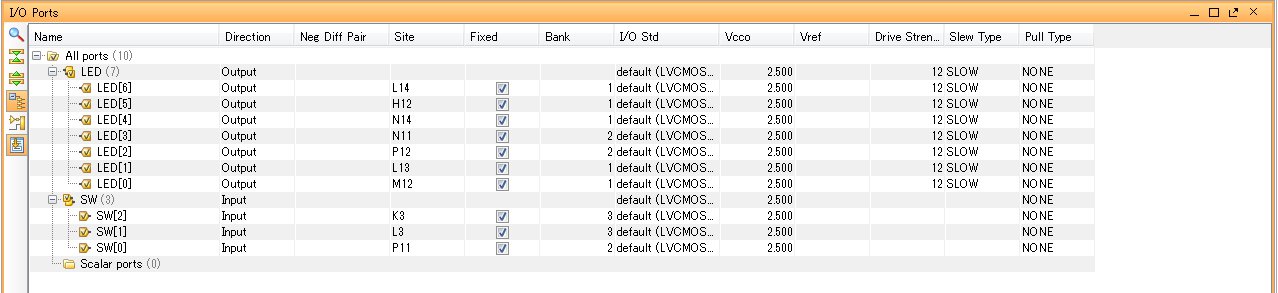

- いくつかダイアログが出ますが、OKしますと、PlanAheadが立ち上がります。ここで、実際のピンと対応付けをしていきます。

今回は大量にピンがあるので、下にあるI/O Portsの画面のSite項目に直接ピン番号を入力しました。横のFixedには自動でチェックが入ります。

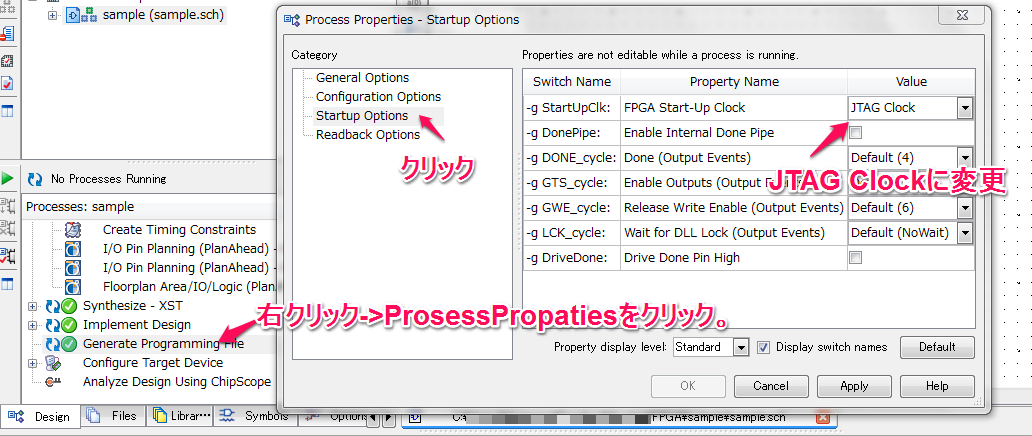

ピンの割り当てが終わりましたら、忘れず保存した上で、PlanAheadを終了させます。 - 元の画面に戻ってきましたら、Generate Programming Fileを右クリック->ProsessPropatiesをクリックします。

プロパティ画面のStartup Optionsより、FPGA Start-UP ClockをJTAG Clockに変更します。

これは、書き込み時"Startup Clock for this file is 'CCLK' instead of 'JTAG CLK'. Problems will likely occur."というエラーが出るのを防ぐ処置です。

bitファイルの作成

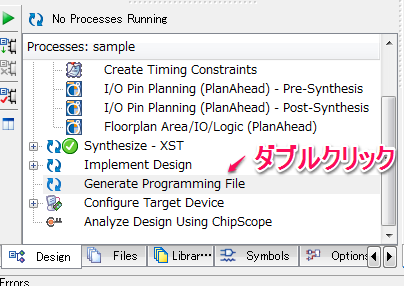

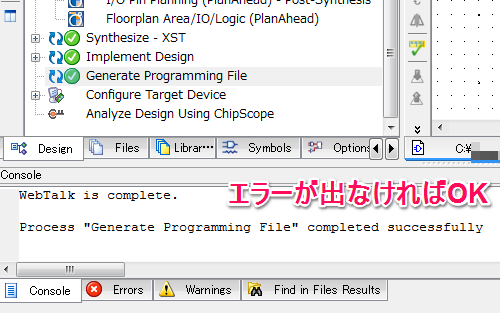

- FPGAに書き込むbitファイルを作成します。

Generate Programming Fileをダブルクリックします。 - ガリガリと論理合成などが走ります。最終的にConsoleにエラーが出ず、"Process Generate Programming File completed successfully"と出ればOKです。

FPGAに書き込み

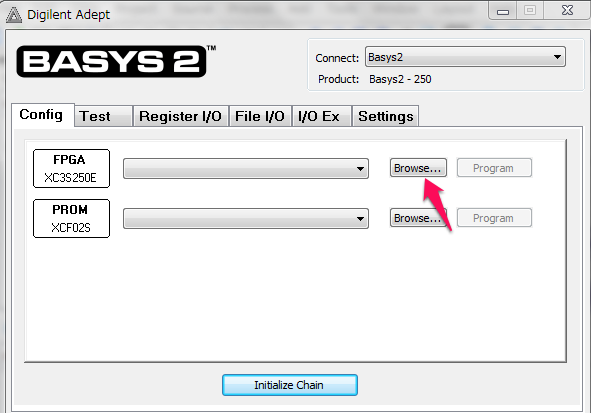

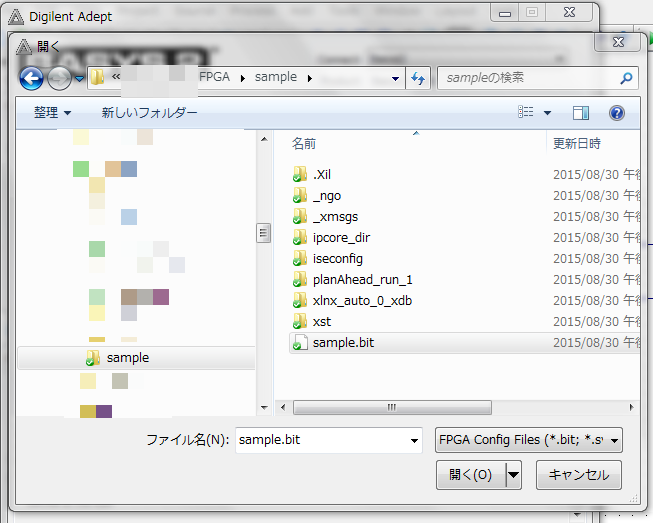

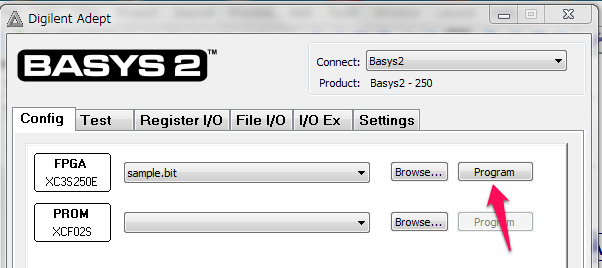

- BASYS2に書き込むためのソフトである、DigilentAdeptを起動し、Configタブより、FPGAに先ほど作成したbitファイルを読み込ませます。

- Programボタンを押し、書き込みをします。書き込みが完了しましたら、バグがなければFPGAが動作しているはずです。

Counter: 742,

today: 2,

yesterday: 0

このページの参照回数は、742です。